# Silicon Photonics COE-CPPICS Technical Digest

Second Edition 20<sup>th</sup> November 2024

Department of Electrical Engineering IIT Madras, Chennai – 600 036 Website: https://cppics.iitm.ac.in/

## Preface

It has been about an year since the first and inaugural technical digest of our Silicon Photonics CoE-CPPICS was released by the Hon'ble Secretary Shri S. Krisnan, MeitY, Govt. of India. During the last vear, we have progressed significantly in terms of demonstrating some landmark experimental results in the domain of quantum photonics and microwave photonics system level applications, contributing towards electronic and photonic design automation (EPDA), developing algorithms for the extraction of silicon photonic wafer-scale manufacturing variabilities, initiating for the development of process design kit (PDK) towards electronic and photonic co-integration, designing DC and high-speed RF PCBs for programmable co-packaged photonic integrated circuits, etc. In addition, our labs have been equipped with a dedicated wafer cleaning station, fully automated silicon photonic wafer scale testing facilities along with a high-performance multichannel quantum photonic measurement system for the last year. All these have been possible because of the collective effort of our entire team CoE-CPPICS and its direct participation and/or in-depth R&D collaboration with multi-national industry partners like Keysight Technologies, Silterra, and izmo Microsystems. A special thanks to my esteemed colleagues Prof. Anjan Chakravorty, Prof. Deleep Nair, Prof. Sankaran Aniruddhan and Prof. Janakiraman Viraraghavan who contributed significantly by training/guiding research scholars and interacting with industry partners on a regular basis by putting their maximum efforts. I also extend my special thanks to MeitY Scientist Dr. SankhaDip Das and R&D Head Smt. Sunita Verma who have been guiding us on a regular basis to execute our committed R&D plan and encouraging us to think beyond, in terms of creating value chain ecosystem for chip-scale manufacturing of photonic integrated circuits and systems to empower digital India.

Once again we would like to put on record that we are enormously grateful to our Director Prof. V. Kamakoti, who has been constantly supporting our R&D by all means. With his far-sight vision and encouragement, we were able to form a very active Industry Advisory Board under the chairmanship of Dr. Mallik Tatipamula (CTO at Ericsson, Silicon Valley, USA), for guiding us to carry out industry relevant R&D activities. The other distinguished members in our CPPICS Industry Advisory Board are industry leaders like Dr. Vivek Raghunathan (Xscape Photonics, USA), Dr. Kishore Kamath (Intel USA), Dr. Steve Johnston (Merck KGaA, Germany), Dr. Prith Banerjee (Ansys USA), Dr. Ravi M. Bhatkal (India/USA Element Solutions), Mr. Narayan Srinivasan (Intel USA), Shri Vijay Janapaty (Broadcom Inc., USA), Shri Vikas Gupta (GlobalFoundries, USA), and Shri Dinanath soni (izmo Microsystems, India). We are also grateful to Dr. Albert Pang (CEO at Silterra Malaysia) who gracefully responded to our invitation and joined as one of the distinguished members of the CPPICS Industry Advisory Board.

Lastly but the most importantly, likewise first edition of technical digest, this second edition is also composed and edited by our research scholars, postdoctoral scientists, and project engineers led by our CTO, Dr. Arnab Goswami. They have organized beautifully their team-wise research contributions which have been carried out during the last one year. Thus we have tried to ensure readers to get a true picture of their intense dedication, team works, passion for scientific research and expressions. I have the fullest appreciation to them for bringing out this 2nd edition of technical digest with in a very short notice period with their greatest level of commitments.

BXM

(Bijoy Krishna Das) Chief Investigator of Silicon Photonics CoE-CPPICS Professor in Dept. of Electrical Engineering, IIT Madras Date: 20<sup>th</sup> November, 2024

# Contents

| 1        | Message from Esteemed Well-Wishers                                                                                                                                                                                                              | 5                                                                                                                                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b> | Major Achievements during Last One Year                                                                                                                                                                                                         | 11                                                                                                                                                        |

| 3        | Silicon Photonics @ IIT Madras: Looking Backward                                                                                                                                                                                                | 12                                                                                                                                                        |

| 4        | Centre at a Glance                                                                                                                                                                                                                              | 18                                                                                                                                                        |

| 5        | Our Experts                                                                                                                                                                                                                                     | 20                                                                                                                                                        |

| 6        | Industry Advisory Board                                                                                                                                                                                                                         | 22                                                                                                                                                        |

| 7        | Team Members                                                                                                                                                                                                                                    | 23                                                                                                                                                        |

| 8        | Organizational Structure                                                                                                                                                                                                                        | <b>25</b>                                                                                                                                                 |

| 9        | Research Labs and Facilities                                                                                                                                                                                                                    | 26                                                                                                                                                        |

| 10       | <ul> <li>State-of-the-Art R&amp;D Activities</li> <li>10.1 Device Design and Compact Modeling</li></ul>                                                                                                                                         | $\begin{array}{c} 28 \\ 28 \\ 28 \\ 31 \\ 34 \\ 34 \\ 37 \\ 39 \\ 41 \\ 41 \\ 45 \\ 50 \\ 52 \\ 54 \\ 56 \\ 59 \\ 62 \\ 65 \\ 68 \\ 68 \\ 71 \end{array}$ |

| 11       | Industry Collaboration         11.1 Foundry Partner - SilTerra Malaysia Sdn. Bhd.,         11.2 System in Package Partner - izmo Microsystems, Bengaluru, India         11.2 EPDA Partner         Kawirkt Tashnalaring         Inc.         USA | <b>74</b><br>74<br>76                                                                                                                                     |

| 12       | 11.3 EPDA Partner - Keysight Technologies, Inc. USA                                                                                                                                                                                             | 77<br><b>7</b> 8                                                                                                                                          |

|          | Publications                                                                                                                                                                                                                                    | 89                                                                                                                                                        |

| 14 Patents                                                    | 94 |

|---------------------------------------------------------------|----|

| 15 Book Chapters                                              | 95 |

| 16 Media Coverages on Silicon Photonics CoE-CPPICS IIT Madras | 96 |

# Message from Esteemed Well-Wishers

Smt. Sunita Verma, R&D Head and Group Coordinator, MeitY, Govt. of India Prof. Veezinathan Kamakoti, Director of IIT Madras Dr. Mallik Tatipamula, CTO at Ericsson Silicon Valley USA Dr. Albert Pang, CEO at Silterra Malaysia Shri Dinanath Soni, Executive Director of izmo Microsystems, India

#### Group Coordinator R&D in Electronics & IT, MeitY, Govt. of India

Sunita Verma भारत मरकार Scientist G & Group Coordinator Government of India R&D in Electronics & IT इलेक्टॉनिकी और सचना प्रौद्योगिकी मंत्रालय stry of Electronics & Information Technology इलेक्टॉनिक्स निकेतन / Electronics Niketan 6, सी जी ओ कॉम्पलेक्स / 6, C G O Complex नई दिल्ली-110003 / New Delhi-110003 दूरभाष / Tele: Website: www.meity.gov.in अ- स- पत्र स. GG-11/15/2020-EMCD The Digital India initiative, a flagship program by the Government of India, has played a pivotal role in transforming the nation into a digitally empowered society and knowledge-driven economy. The advancement of silicon photonics and quantum technologies is crucial for India's future in tech-driven innovation. At IIT Madras, the Ministry of Electronics and Information Technology (MeitY) has supported the establishment of the Centre for Programmable Photonic Integrated Circuit and Systems (CPPICS). Launched in December 2020, this centre is dedicated to designing, manufacturing, and developing applications with Programmable Photonic Integrated Circuit (PPIC) using silicon photonics. This report captures CPPICS's strides in advancing such devices, essential for creating faster and more energy-efficient devices in data processing, digital computing, and next-generation quantum technologies. CPPICS has made significant progress in designing and demonstrating state-of-the-art photonic devices, including Quantum Key Distribution transceivers and programmable photonic architectures. These advancements position us at the forefront of research essential for secure, scalable quantum systems. Key collaborations with industry leaders, such as Keysight Technologies, Silterra, and iZMO Microsystems, have strengthened our ability to transition from research to application. This technology and the associated ecosystem will support Indian sectors in quantum computing, 5G/6G communications, IoT, radar, avionics, and more. CPPICS aligns with the "Atmanirbhar Bharat" vision of Government of India. We at MeitY truly believe the centre is now ready to compete with the global state-of-the-art which can serve these country's needs decades to come. I extend my best wishes to the center for successfully advancing the technology toward full commercialization and paving the way for PIC manufacturing in India. ELECTRONICS INDIA

#### **Director of IIT Madras**

Indian Institute of Technology Madras Chennai – 600 036

Phone: 0091-44-2257 0694 / 0091-44-2257 8001 Fax : 0091-44-2257 8003 / 0091-44-2257 0509

प्रो. वी. कामकोटि Prof. V. Kamakoti निदेशक Director

भारतीय प्रौद्योगिकी संस्थान मद्रास चेन्नै — ६०० ०३६ Email : kama@cse.litm.ac.in / director@iitm.ac.in Web : http://www.litm.ac.in

MESSAGE

I am delighted that the R&D team CPPICS is releasing its 2nd Technical Digest showcasing recent progress in the niche areas of CMOS fabrication process compatible silicon photonics technology. As our Country is moving towards building our own capability in the area of Semiconductor Electronics, it is very heartening to see our Institute establish a Centre of Excellence in Silicon Photonics, which is an outcome of extensive R & D pursued over nearly two decades. The substantial seed funding for establishing this state-of-the-art Silicon Photonics Centre of Excellence on Programmable Photonic Circuits and Systems (CPPICS) by the Ministry of Electronics & Information Technology (MeitY), Govt. of India has helped in the **consolidation of indigenously developed silicon photonics technology at IIT Madras. Within a** very short span of time the team has strengthened its research collaboration with industries like Keysight Technologies, Siltera and iZMO Microsystems. My heartiest congratulations to the entire R&D team of CPPICS headed by Prof Bijoy Krishna Das. I am confident that the centre is going to impact significantly, both in the domestic as well as global silicon photonics R & D market in the upcoming years.

U. he makohi (V. Kamakoti)

#### CTO of Ericsson, Silicon Valley, USA

November 18, 2024

Industry Advisory Board Chairman - Message

In an era where the convergence of connectivity (5G/6G), compute, control (AI), and sensing shapes the technological landscape, the demand for ultra-fast, energy-efficient, and scalable systems has never been greater. Leading this transformation is the field of Photonic Integrated Circuits (PICs), leveraging the speed and bandwidth of light to overcome traditional system limitations.

Reflecting on the exceptional progress of CPPICS at IIT Madras, I feel immense pride and optimism. By advancing silicon photonics and pioneering programmable architectures, the Centre is setting benchmarks in computing, telecommunications, and sensing, with the potential to revolutionize fields such as 6G, cloud computing, autonomous systems, and manufacturing.

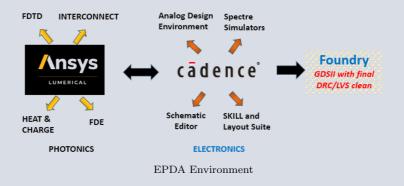

Under the visionary leadership of Prof. Bijoy K. Das, CPPICS has become a hub of excellence. The adoption of a Research, Development, and Manufacturing Model exemplifies a forward-thinking approach, bridging research with impactful applications. Key collaborations, including partnerships with Keysight Technologies and Silterra, highlight the Centre's industry relevance. The upcoming launch of the Electronic-Photonic Design Automation (EPDA) tool, developed with Keysight and integrated into the ADS platform, underscores the ingenuity and dedication of the CPPICS team.

Congratulations to the faculty, students, and staff at CPPICS for your outstanding achievements. Your dedication has established the Centre as a leader in photonic innovation. As Chairman of the Industry Advisory Board, I'm honored to work with an exceptional board to support CPPICS's mission. Together, we're driving transformative innovation in photonics and electronics. Let's continue pushing boundaries and shaping the technologies of tomorrow.

With best wishes for an even brighter year ahead,

Yours sincerely,

Mallikarjun Tatipamula, Ph.D, FREng Chief Technology Officer, Ericsson Silicon Valley

2755 Augustine Dr., Santa Clara, CA 95054

#### CEO at SilTerra Malaysia

# SILTERRA®

November 19, 2024

#### Message from Dr Albert Pang Shu Koon, CEO of SilTerra

I am honored to serve as an Industry Advisory Board member for the CoE-CPPICS, a leading R&D organization in the field of silicon photonics, a dynamic field shaping the future of communications, sensing technologies, computing, among other things.

My fervent hope is for CoE-CPPICS to serve as a platform for disseminating cutting-edge research and inspiring innovation in its areas of expertise. By intensifying multidisciplinary collaboration and cross-training between academia and industry, I believe, the impact of meaningful research work in the area of silicon photonics will be further accelerated.

SilTerra is committed to supporting the on-going collaboration with CoE-CPPICS in promoting groundbreaking work that not only advances scientific understanding but also finding viable solutions to address current and future market needs. Thus, let us continue working together to expand the boundaries of innovation.

Best wishes,

Sincerely,

Dr. Albert Pang, Ph.D, Electrical Engineering, Chief Executive Officer, SilTerra Malaysia Sdn. Bhd.

#### Executive Director, izmo Microsystems, Bengaluru

# izmo

#### Message

I am delighted that Team COE-CPPICS is releasing it's 2<sup>nd</sup> Edition of the Technical Digest showcasing the significant progress made in the development of CMOS based silicon photonics technology, achieving lower power consumption and high data throughput.

It has been a year since the Centre for Programmable Photonic Integrated Circuits and Systems at IIT-M got recognised as the Centre for Excellence for Photonics in India by the Ministry of Electronics and Information Technology (MEITY). It was started with a substantial funding by MEITY in the beginning of 2021 with the mission of "Atma Nirbhar Bharat", building the capability within the country in the development and manufacturing of Silicon Photonics Integrated Circuits.

In the advent of artificial intelligence/machine learning and the global demand made on High Power Computing, quantum computing is the need of the hour. Silicon Photonics is critical for rapid data growth and supporting high band width applications. CPPICS R&D team has made significant strides in meeting these technology challenges that would result in lower cost per bit.

All that, in a very short span of time.

Once again, congratulations to Team COE-CPPICS on the remarkable achievements.

anathe Jouri

Dinanath Soni Executive Director izmo Microsystems

izmo Microsystems Private Limited Ashok Arcade, Plot Nos. 51 & 52, EPIP Industrial Area, Whitefield, Bangalore- 560066, India CIN No.: U26101KA2023PTC182295

# Major Achievements during Last One Year

(November 2023 - October 2024)

- MoU & SoW signed with SilTerra for advanced level silicon photonics technology development

- MoU & SoW signed with Keysight Technologies for EPDA development to be launched under Keysight ADS platform.

- MoU signed with Hyderabad based startup company amPICQ for joint collaboration and technology transfer

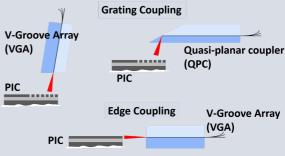

- In-house development of fiber attachment process with grating coupler integrated PICs with quasi-planar couplers (QPC), vertical grooved arrays (VGA) and standard single optical fibers.

- Generation of single photon pairs from microring resonators and demonstration of time-energy entanglement

- In-house demonstration of distributed Bragg reflector based ASE noise removal pump wavelength filters for futuristic chip-scale quantum photonic circuits

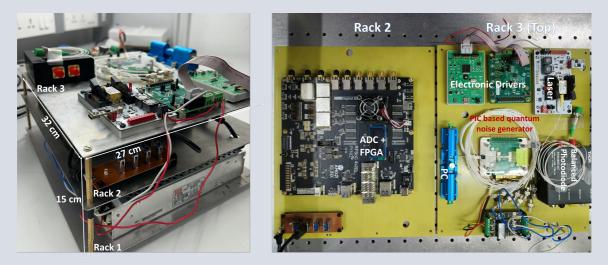

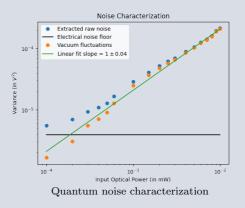

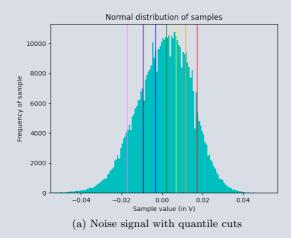

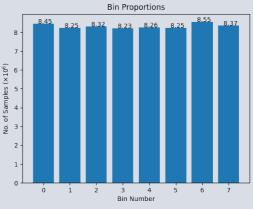

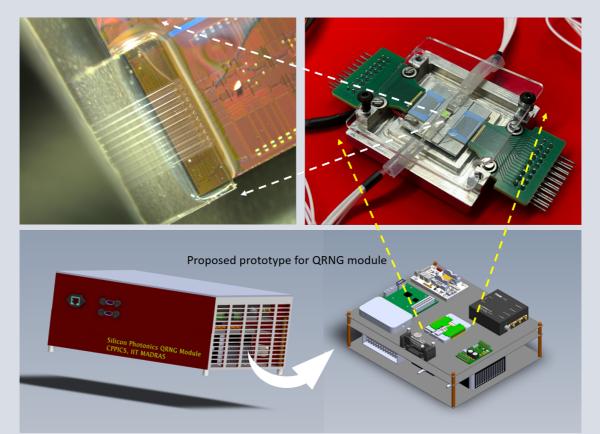

- Demonstration of working prototype of a standalone PIC based QRNG module

- Successful in-house demonstration of low-loss silicon nitride waveguides (~ 0.15 dB/cm) and high-Q microring resonators (Q~  $1.7 \times 10^6$ )

- Demonstration of SiN-OSP based tunable optoelectronic oscillator (upto 20 GHz) for wireless communication and radar systems.

- First-level demonstration of fully integrated microwave photonic filter with on-chip modulator, optical signal processor and photodetector.

- Proof-of-concept demonstration of programmable photonic integrated circuit (PPIC) based X-band radio over fiber (RoF) receiver link.

- R&D Consortium on Silicon Photonic Enabled Quantum Circuits and Systems (SPEQCS) comprising experts from The Institute of Mathematical Sciences (IMSC), Society for Electronic transaction and security (SETS), izmo Microsystems Bengaluru, and IIT Madras.

# Silicon Photonics @ IIT Madras: Looking Backward

(Aug. 2006 - Dec. 2020)

Though the interests in silicon photonics research among Indian scientists and engineers were noticeable here and there, no planned long-term research goals were set until IIT Madras took the lead to start a silicon photonics research group in 2006. Since then the group at IIT Madras has been actively engaged in novel design, fabrication and characterizations of silicon photonic devices for communication systems and sensor applications. By the end of 2011, various prototype devices were demonstrated by making use of conventional i-line lithography technology  $(1-\mu m node)$  available at IIT Madras. With the availability of nanofabrication facilities at the Centre for NEMS and Nanophotonics (funded by MeitY Govt. of India), the research program was raised to the next higher level – research outcomes have been presented in international conferences, published in peer reviewed journals, and filed as patents as well. The goal of the research group is now set to carry out world class silicon photonics research encompassing novel device designs, CMOS compatible fabrication process optimizations and experimental demonstrations leading towards cost-effective, multi purpose programmable photonic processor chips for microwave and quantum photonic engineering applications. The *Silicon Photonics CoE-CPPICS* is the latest addition in our timeline. Some landmark glimpses of our journey are highlighted below.

Landmark 2007: The first silicon photonic device characterization setup was developed jointly by our first MS Research Scholar Rupesh Navalakhe (jointly guided by Prof. Nandita DasGupta) and first PhD Research Scholar Shantanu Pal in the OCEAN Lab. The optical bench was placed on the top of a coconut coir bed for vibration isolation. All the components used to build this setup was collected from the storage (left over from Prof. Raina) except the IR CCD camera on the extreme right which was bought from the seed grant of Rs. 5 Lakhs from IIT Madras.

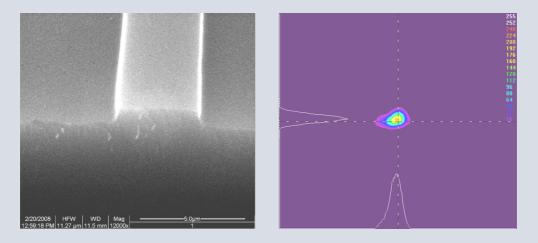

Landmark 2008: The first single-mode waveguide was fabricated at the Microelectronics & MEMS Lab using silicon-on-insulator (SOI) substrate with a device layer thickness of 5  $\mu$ m. The guided mode was captured by the IR CCD camera which is also shown here.

Landmark 2009: The number of students and research scholars increased to a team of eleven and we started calling it as the Integrated Optoelectronics Group. The Integrated Optoelectronics Lab was built in Room No. CSD106.

Landmark 2011: Some working silicon photonic prototype devices fabricated at IIT Madras were fiber-pigtailed and packaged in SAMEER, Mumbai. The project was funded by the Department of Information Technology (DIT), Govt. of India.

Landmark 2012: When the whole world was progressing fast in the area of silicon photonics technology by taking advantage of their advanced nano fabrication facilities, our PhD research scholar Sujith Chandran was trying desperately to demonstrate photonic wire waveguide using age-old microelectronics fabrication facilities at IIT Madras. However, his efforts finally led to the filing of a US patent, which was granted at a later date.

Landmark 2012: Finally, the Centre for NEMS and Nanophotonics (CNNP) was funded by the Department of Electronics and Information technology (DeitY), Govt. of India and our silicon photonics technology started evolving very fast by the hard works of a dedicated team of research scholars led by Sujith Chandran and P. Sakthivel.

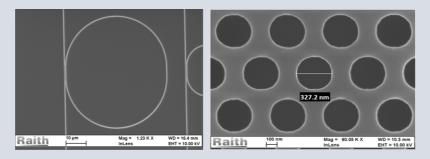

Landmark 2015: The first photonic wire waveguide based microring resonators (MRRs) and photonics crystal structures were demonstrated in silicon-on-insulator (SOI) with device layer thickness of 220 nm (CMOS photonics foundry compatible) using CNNP facilities.

Landmark 2017: A specially designed microring resonator was fabricated to demonstrate evanescent field induced refractive indexing sensing purpose. This was the first silicon photonic wire waveguide device used for lab-on chip sensing application using fiber-optic grating coupling setup in our Integrated Optoelectronics Lab (now moved into CSD108).

Landmark 2019: Almost all the CMOS fabrication process compatible silicon photonic basic building blocks were demonstrated using in-house fabrication facilities; some of them are with novel design architectures and can be directly used for programmable photonic integrated circuits.

Landmark 2020: The Silicon Photonics Centre of Excellence - Centre for Programmable Photonic Integrated Circuits Systems (Silicon Photonics CoE-CPPICS) was proposed with an ambitious list of objectives. It was granted on 29th December 2020 and in midst of Covid'19 Pandemic, the team CoE-CPPICS started working on programmable silicon photonic processors following product research and manufacturing model.

# Centre at a Glance

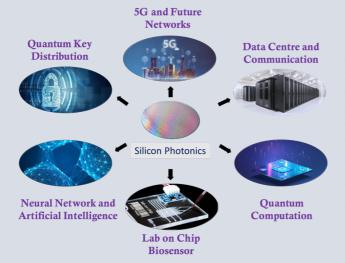

The Centre for Programmable Photonic Integrated Circuits and Systems (CPPICS) is one of the centre of excellence (CoE) initiatives by the Ministry of Electronics and Information Technology (MeitY), Govt. of India. It is hosted by the Department of Electrical Engineering, IIT Madras with a long-term mission for catering R&D in the area of programmable photonic integrated circuits and systems using CMOS compatible silicon photonics technology for solving various levels of complex problems.

#### **Background and Funding Status**

The CoE-CPPICS has been established on 1st January 2021 in the Department of Electrical Engineering, IIT Madras with a substantial seed funding of Rs. 2,665 Lakhs (USD 3.5M) from the MeitY, Govt. of India, (Sanction No. GG-11/15/2020/EMCD, dated 29.12.2020), in-kind contribution of Rs. 325 Lakhs (USD 0.5M) from the izmo Microsystems Bengaluru and subsequent additional funding of Rs 425 Lakhs (USD 0.7M) from IIT Madras. This recognition and funding has been possible because of 17 years (since 2006) of R&D work by the Integrated Optoelectronic Research Group led by Prof. Bijoy Krishna Das in the area of silicon photonics technology.

#### Mission

Our mission is to build capacity in all verticals of silicon photonic integrated circuits manufacturing eco-system through focused R&D and nurture Indian photonics industry for immediate needs in domestic and international markets.

#### Silicon Photonics CoE-CPPICS Inaugurated on 20th October 2023

The inauguration of our Silicon Photonics Centre of Excellence, graced by the esteemed Shri S Krishnan, Secretary of the Ministry of Electronics and Information Technology (MeitY). This event was further graced by the august presence of Prof. Kamakoti Veezhinathan, Director of IIT Madras and other distinguished individuals, including Smt. Sunita Verma, Scientist G and R&D Group Coordinator (MeitY), Dr. Sankha dip Das, Scientist D (MeitY), Prof. Nagendra Krishnapura (Head of the Department of Electrical Engineering, IIT Madras), Dr. Kishore Kamath, (Vice President of R&D silicon photonics product division, Intel, USA), Dr. Ravi Bhatkal (Managing Director of India Element Solutions Inc, India), Mr. Dinanath Soni (Executive Director of izmo Microsystems, India). Prof. Bijoy Krishna Das, Chief Investigator, Silicon Photonics CoE-CPPICS, IIT Madras, mentioned, "The Silicon Photonics CoE-CPPICS is forging critical partnerships including a strong collaboration with M/s izmo Microsystems in Bengaluru, to deliver state-of-the-art System-in-Package solutions for silicon photonic processor cores. This transformative technology is primed to cater to a wide array of sectors, including quantum computing, quantum communication, 5G/6G communications, IoT, radar, avionics, and more. The nation is looking forward to witnessing the success of CPPICS as it takes this technology to full commercialization and spearheads PIC manufacturing in India. Team CoE-CPPICS has tied-up with SilTerra Malaysia Sdn. Bhd. Silicon Photonics Foundry, Malaysia for wafer scale yield testing of some novel silicon photonic devices already demonstrated using in-house technology at IIT Madras. The team has also signed a MoU with Keysight Technologies USA for joint R&D activities in the area of Silicon Photonics technology".

#### **Current Research Activities**

The immediate focus of this CoE is to provide better solutions for microwave and quantum photonics applications such as advanced photonic processors to be used in high-performance RF transceivers, scalable linear optical quantum computing processors for the nextgeneration qubit computation, and chiplevel quantum key generation and distribution circuits, etc. CPPICS is actively developing indigenous PIC design rules and hardware infrastructure for precision packaging for system-level applications.

Quantum Information Processing

- Quantum Random Number Generation

- Quantum Key Distribution

- Quantum Sampling Algorithm

Microwave Photonics

- Programmable Radio Frequency Filter

- Optoelectronic Oscillator

- Photonic Beamforming

In our unwavering commitment to driving innovation and fostering technological advancements, we, at the Center of Excellence, are actively engaged in pioneering research starting from technology development to packaging solutions. Our expertise spans a diverse spectrum of domains, with esteemed faculty members from IIT Madras playing an integral role. Their invaluable guidance and expertise are essential to our research endeavors.

# **Our Experts**

# Chief Investigator

Prof. Bijoy Krishna Das

The center is being led by Chief Investigator Prof. Bijoy Krishna Das, steering CPPICS toward excellence in research and innovation. Since August 2006, his dedicated efforts have been instrumental in spearheading the development of inhouse silicon photonics device technology at IIT Madras.

## **Chief Technology Officer**

Dr. Arnab Goswami

Arnab Goswami joined as the Chief Technology Officer (CTO) of the centre in January 2022. He has been involved in the overall lab infrastructure development, fabrication process development, supervising design and foundry tape-outs. He is also responsible for the creation and execution of self sustenance plan and techno-commercial roadmaping.

## **Co-Investigators**

**Prof. Enakshi Bhattacharya** MEMS & Photonics

**Prof. Amitava DasGupta** Device Modelling & VLSI

**Prof. Anil Prabhakar** Quantum Photonics

**Prof. Anjan Chakravorty** Compact Modelling

**Prof. Deleep R. Nair** Design, Fab and Testing

**Prof. Deepa Venkitesh** Fiber Optics & RF Photonics

**Prof. Janaki Viraraghavan** Digital IC Design

**Prof. Sankaran Aniruddhan** Analog IC design

**Prof. Sudharsanan S** Photonics Technology

**Prof. Sargunaraj Christopher** Microwave Engineering

# Industry Advisory Board

#### Chairman

As the chairman of CPPICS Industry Advisory Board, I am committed to coordinate with other board members to provide guidance to the team CoE-CPPICS to continue its activities following the Product Research Development and Manufacturing model.

Mallik Tatipamula CTO at Ericsson San Jose, California, USA

**Members**

**Albert Pang** CEO SilTerra, Malaysia

**Dinanath Soni** Executive Director izmo MicroSystems, India

Vivek Raghunathan Founder & CTO Xscape Photonics Inc., USA

Arjun Kumar Kantimahanti R&D Engineer (Optical Systems Division) Broadcom, USA

**Prith Banerjee** CTO, Ansys Inc. Palo Alto, California, USA

Vikas Gupta Senior Director GlobalFoundries USA

*Kishore Kamath* Vice President R&D, Intel Corporation, USA

**Kailash Narayanan** President & General Manager Keysight Technologies, USA

Ravi M. Bhatkal Managing Director MacDermid Alpha Electronics Solutions, India

Narayan Srinivasa Director Intel Corporation USA

Steve Johnston Vice President Merck KGaA Darmstadt, Germany

Vijay Janapaty Vice President & General Manager Broadcom Inc., USA

Silicon Photonics CoE-CPPICS IIT Madras

# **Team Members**

## **Postdoctoral Researchers**

Nagarajan Nallusamy Nonlinear Photonics & PIC Packaging

Shamsul Hassan QRNG & PIC Packaging

# **PhD Scholars**

Suvarna Parvathy High-Speed Modulator

Ashitosh Velamuri Microwave Photonics & Compact Modeling

Ram Mohan Rao Boyapati Quantum Key Distribution

Anushka Tiwari SiN Technology Development & Optoelectronic Oscillator

Riddhi Goswami SiN Technology Development & Photonic Beamforming

Ankan Gayen QRNG & PIC Packaging

Pawan Kumar Pandit

Feedback Control

Kumar Piyush Programmable Photonics & EIC-PIC Co-Integration

Yash Raj Programmable Photonics & **Boson Sampling**

Dibyanchal Sahu **EIC-PIC** Integration

Anjana James Compact Modeling & PDK Development

Mayukh Mandal Integrated Quantum Photonics

Sarad Subhra Bhakat Si-SiN Hybrid Integration & SiN technology Development

Shuruti Pandey Compact Modeling & PDK Development

# MS(Res.)/M.Tech Scholars

**Pranita Kumari Swain** SiN Technology Development & Non-Linear Photonics

Akash Shekhar EIC-PIC Integration

Manu Maxim Electronic Oscillator

Rahul Krishna K Neuromorphic Computing

Chaganti Kamaraja Siddhartha QRNG

# **Project Staff**

$\begin{array}{l} \textit{Vinoth S} \\ \textit{PIC Packaging} \end{array}$

# Administrative Secretary

B. Sindhura

# Lab Technicians

Mr. P Saranath

D M Sathish Dev

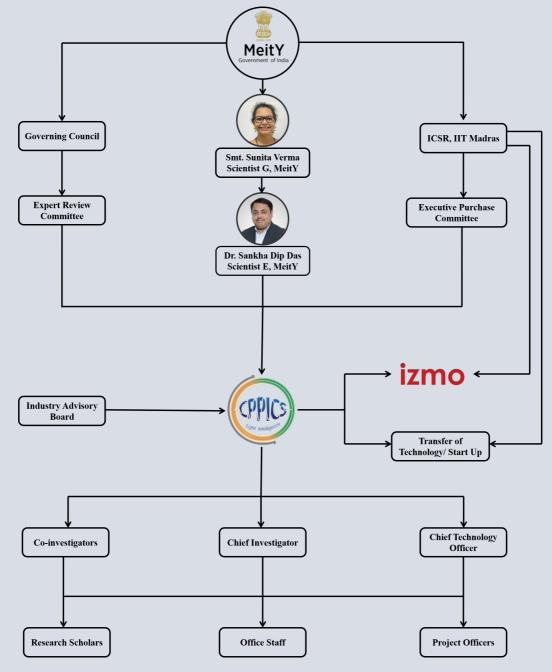

# **Organizational Structure**

This CoE Organization is composed of a Governing Council featuring esteemed members, an Expert Review Committee with exceptional expertise in similar and versatile research areas, Principal and Co-Investigators representing the renowned institution IIT Madras, ICSR – IIT Madras, a Chief Technology Officer, Academic and Industry veterans as collaborators, dedicated and proficient research scholars, dynamic Project Officers, and skilled office staffs.

# **Research Labs and Facilities**

In January 2021, our team embarked on an ambitious journey to transform a standard laboratory space into a state-of-the-art design and characterization facility. At CPPICS, we are committed to pushing the boundaries of light-based technologies. Our advanced research facilities and cuttingedge design tools empower researchers and scholars to unlock the immense potential of photonic integrated circuits.

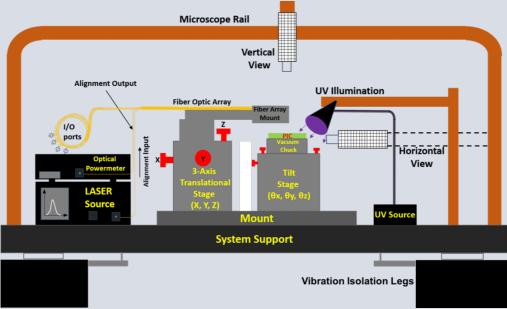

Fully automatic silicon photonics probe station

CPPICS characterization lab

Edge coupling set up

Research scholars during experiments

Research scholars in fabrication process lab

In addition to CPPICS's own facilities, we have in-house fabrication facilities at Center for NEMS and Nanophotonics (CNNP), IIT Madras. The cleanroom within CNNP spans over 2500 square feet and is equipped with state-of-the-art systems for deposition, lithography, etching, and characterization. This robust infrastructure enables us to conduct cutting-edge research and development while maintaining high standards of precision and quality.

- Electron-Beam Lithography

- DUV and i-line Lithography Systems

- Laser Mask Writer

- LPCVD and PECVD Systems

- Chemical Mechanical Polishing

- Oxidation and Diffusion Furnaces

Major Characterization Equipment

Major Process facilities

- 8 channel superconducting Nanowire Single-Photon Detector System

- Lightwave Component Analyzer and Vector Network Analyzer (26.5GHz & 50 GHz)

- High-Resolution Optical Spectrum Analyzer(Resolution Bandwidth 0.04 pm)

- Real-time Digital Oscilloscope (50 GHz)

- Arbitrary Waveform Generator (50 GHz)

- Wafer-scale silicon photonics probe station

Wafer-scale silicon photonic probe station

# State-of-the-Art R&D Activities

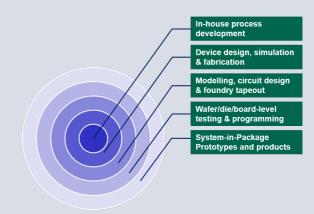

At CoE-CPPICS, we drive innovation in photonic integrated circuits through comprehensive R&D, spanning simulation, device design, prototyping, and testing. Our expertise includes compact modeling, waveguide technology on SOI, SiN, and hybrid platforms, as well as device and circuit design. We excel in optimizing programmable photonic circuits for microwave photonics, quantum photonics, and computational applications. In addition, we focus on seamless photonic system integration, emphasizing electronic-photonic cointegration, fiber-optic attachment, and advanced packaging.

#### **Device Design and Compact Modeling**

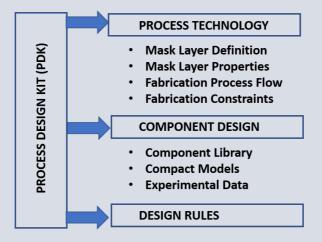

To successfully scale photonic circuits, it is important to analyze the behavior of each device. Creating compact models for basic building devices is crucial. This process empowers photonic designers to develop process design kits (PDKs) and simulate circuits and systems for different applications.

#### **Compact Modelling of Silicon Photonic Devices**

# Associated Research Scholars: Shruti Pandey, Anjana James, Ashitosh Velamuri, Suvarna Parvathy, Pawan Kumar, Nagarajan Nallusamy, Shamsul Hassan

Our group is actively involved in the compact model development of various active and passive photonic components on a chip as well as wafer-scale process variability extraction.

#### **Device modeling: Passive Devices**

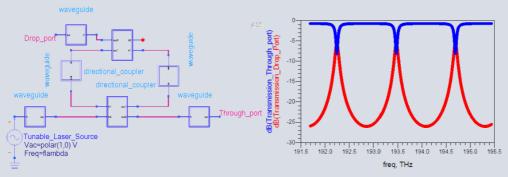

Passive devices like waveguides, directional couplers, ring resonators in all-pass and add-drop configurations, and Mach-Zehnder interferometers are modeled for Spice simulation in EDA tools, which makes it much more time efficient and user-friendly.

Add-drop ring resonator simulated in ADS

#### Device modeling: Active Devices

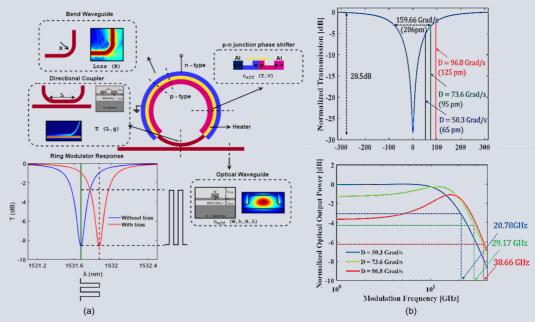

The modulator and photodetector are important components for the realization of an RF photonic link. An accurate model linking the device performance to the design parameters of the device will help the designers to design without going through time-consuming photonic and charge simulations. After running a lot of optical and electrical simulations, we have implemented a preliminary model to give us the linear and non-linear response of the modulator and photodetector. The AC and DC responses of both devices are simulated using our model, and the results are given in the figures below.

Microring modulator compact model: Individual components are separately modeled and combined for the microring modulator system-level model

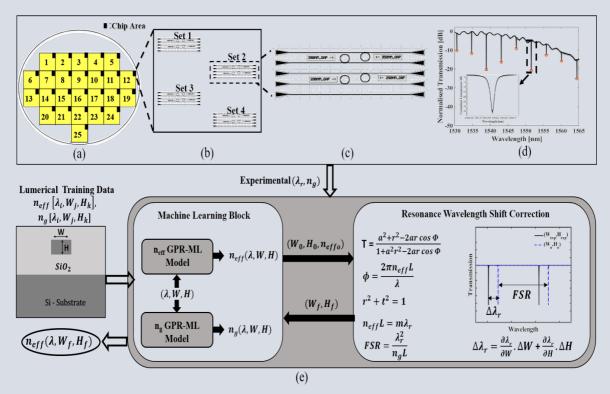

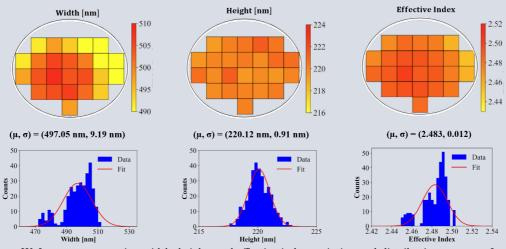

#### Wafer-scale process variability extraction

A Machine Learning (ML)-enhanced algorithm has been developed for the prediction of fabrication process-induced wafer-scale (200-mm) variability, which is computationally faster and has high accuracy in predictions. The algorithm proposed for the prediction of waveguide dimensional variability (and effective index of guided mode) uses data from the experimental characterizations of the racetrack microring resonator (MRR) in an all-pass configuration fabricated across a 200mm silicon-on-insulator (SOI) using the SilTerra silicon photonics fabrication process line. The algorithm is described in the figure above. Wafer-scale width, height, and effective are obtained using the proposed algorithm.

ML enhanced algorithm for wafer scale process variability extraction: (a)Reticle numbering and relative location of devices; (b)Layout; (c) zoomed layout; (d) typical spectral response of the MRRs; and (e) flowchart representing the proposed algorithm with the relevant equations used.

Wafer-map representing width, height, and effective index variation and distribution across wafer.

We also look forward to realizing electronic photonic co-simulation using electronic design automation tools to simulate large-scale electro-optic circuits for applications like LIDAR, neuro-morphic computing, and quantum computing.

#### **Process Design Kit Development**

Associated Research Scholars: Arnab Goswami, Pawan Kumar, Ashitosh Velamuri, Kumar Piyush, Ram Mohan, Suvarna Parvathy

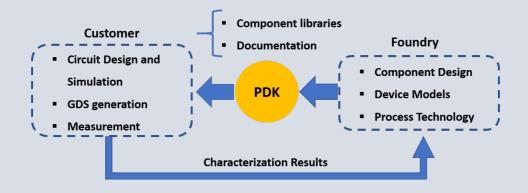

A Process Design Kit (PDK) bridges circuit designers and foundries, enabling efficient photonic circuit design and fabrication. It includes process details, fabrication constraints, and a library of analytical or physics-based models for passive (e.g., waveguides, splitters, grating couplers) and active (e.g., modulators, photodetectors) components. Designers use these libraries to create GDS layouts for fabrication and, in large-scale designs, simulate circuit performance using PDK-compatible blocks before fabrication. The PDK also incorporates experimental data, design rule checks, and is continually updated based on characterization results of fabricated devices to ensure accuracy and compatibility.

PDK serves as a link between the circuit designer and the foundry enabling the circuit designer to design photonic circuits using the different components available in the component library. The component library is in the form of analytical or physics-based models for the basic passive (waveguides, waveguide bends, power splitters, grating couplers) and active (modulator, photodetector) photonic devices. Based on these available component libraries, the customer designs the GDS layout and submits the design to the foundry for fabrication. For large-scale photonic circuit design, there can be PDKs that offer photonic circuit simulator-compatible blocks, which will enable the designer to evaluate the circuit performance well before the actual fabrication. The layout of the desired circuit is shared with the foundry, following which mask preparation and fabrication are carried out. Based on the characterization results of the fabricated devices, required updates are made to the existing PDK.

#### SilTerra joins hands with CPPICS

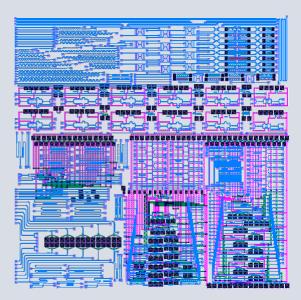

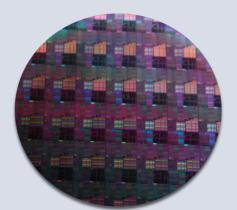

One of the leading global semiconductor foundries, SilTerra, Malaysia has joined hands with CPPICS to develop silicon photonics PDK. For our first run of tape out, our scholars have designed different passive components which includes waveguides, waveguide bends, power splitters, wavelength filters and Mach Zehnder Interferometers. The structures given for tape out have been fabricated by SilTerra, and the optical characterization of the fabricated devices is actively being carried out at CPPICS. These characterization results will be modeled to form our first-cut PDK for SilTerra. This run will be followed by active device fabrication, characterization, and modeling. We are also looking forward to developing models for devices like distributed Bragg reflectors (DBR), waveguide crossings and microring based filters which are not available currently in any other existing foundry PDK.

Layout design of various active and passive devices on 8 mm  $\times$  8 mm chip, for tape-out from SilTerra

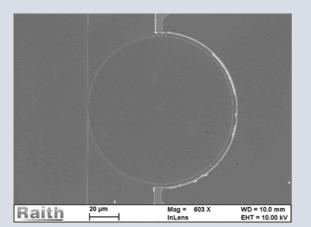

8 inch wafer fabricated at SilTerra, Malaysia

Microscopic image of fabricated unbalanced MZI with reference waveguide

Microscopic image of fabricated directional coupler

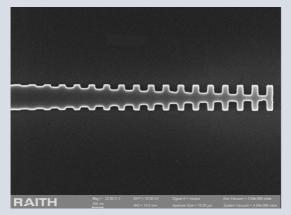

Microscopic image of fabricated distributed Bragg reflector

Microscopic image of fabricated microring resonator with grating couplers

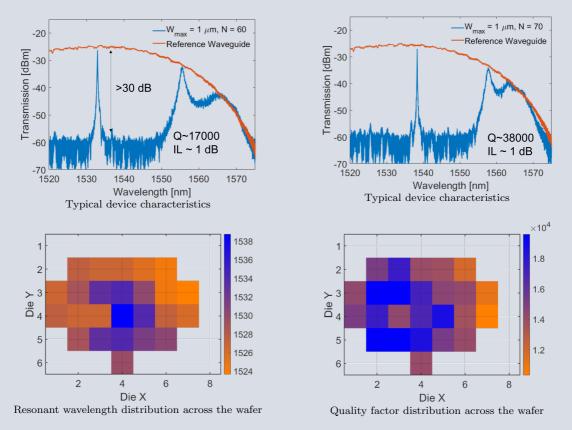

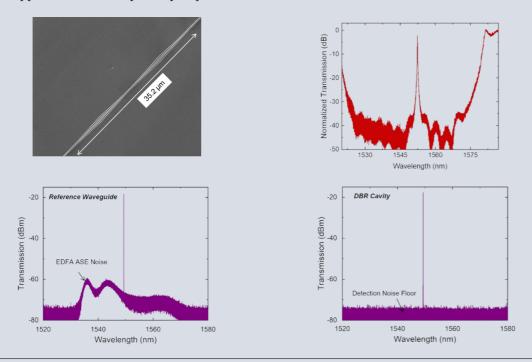

We demonstrated a compact singly resonant DBR cavity with broadband DBR mirrors using SilTerra's 200 mm silicon photonics foundry process line. The wafer-scale yield has been analyzed in terms of resonance wavelength and quality factor.

The standard deviation of the resonant wavelength and quality factor is found to be 3.735 nm and 2650 respectively. The fabrication yield comes to reasonably good but there is a scope for improvement by fine tuning the design and process parameters. Nevertheless, these results are promising for the future inclusion of a DBR-based Fabry-Pérot resonator in the device libraries of commercial silicon photonics PDK, as various active and passive components for large-scale integration.

#### **Fabrication Process Development**

We at CoE-CPPICS are working in two different technology platforms i.e. Silicon on Insulator (SOI) and Silicon Nitride on Insulator (SNOI). Over the past 15 years, we have achieved a high level of maturity in SOI waveguide technology processes. This advancement has allowed us to demonstrate various innovative passive devices, circuits, and phase shifters for multiple applications, maintaining a waveguide loss of less than 5 dB/cm. For the past 2 years, we have been involved in developing in-house SNOI waveguide technology process starting from bare silicon wafer, growing silicon di-oxide on it, followed by LPCVD silicon nitride deposition. Very recently, we have achieved the low loss waveguide with propagation loss below 1 dB/cm. To further reduce the loss we are working constantly to refine our fabrication process steps and have also started working on damascene process. Furthermore, we are also actively working towards the hybrid integration of Si and SiN to demonstrate efficient circuits in terms of lower loss and thermal budget.

#### SOI Waveguide Technology

#### Associated Research Scholars: Suvarna Parvathy, Ram Mohan, Arnab Goswami, Ashitosh Velamuri, Ankan Gayen, Kumar Piyush, Pawan Kumar, Yash Raj

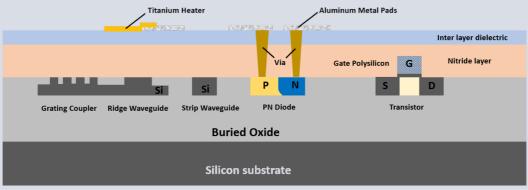

SOI wafers consist of a thin layer of silicon (the device layer), buried oxide and silicon substrate stacked one above another as shown below. The thin silicon layer is used to fabricate waveguides and other passive or active optical devices. The buried oxide prevents propagation of light into the silicon substrate thereby supporting optical modes in the device layer guided by total internal reflection.

| Thin Silicon Layer | $\sim 220 \ nm$    |

|--------------------|--------------------|

| Buried Oxide       | $\sim 2 \ \mu m$   |

| Substrate Silicon  | $\sim$ 500 $\mu m$ |

|                    | Buried Oxide       |

SOI wafer

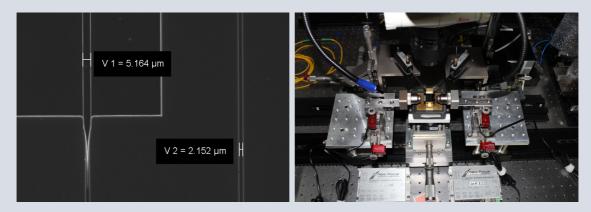

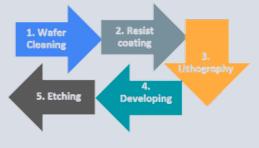

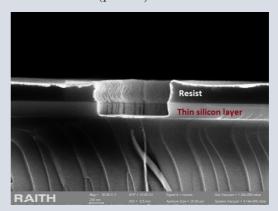

Fabrication flow of optical devices on SOI includes several process steps. We have shown the major steps here. First, we start with cleaning of SOI wafer which includes standard organic cleaning to remove oils followed by inorganic cleaning to remove metallic oxides. After cleaning we need to dehydrate the wafer to remove any water content. Now, we can go for resist(positive/negative) coating. Afterwards on this coated sample, pattern is transferred from mask either using E-beam lithography or photo-lithography.

Once, the pattern is transferred, this wafer is put into developer solution to remove the exposed/unexposed resist (depending on resist type). After developing we go for etching to get our final devices (passive).

SEM cross-section view of etched device on SOI

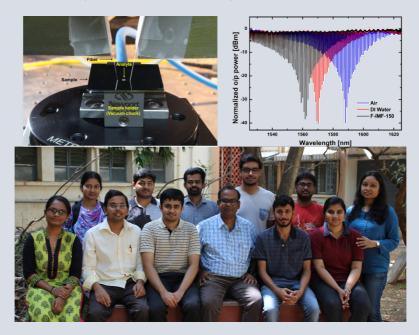

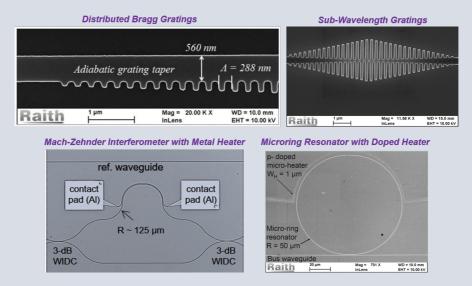

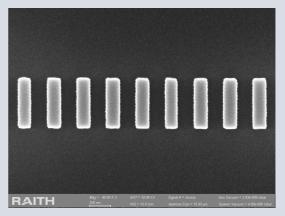

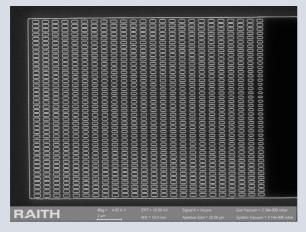

The core research of our group involves novel device designs, CMOS compatible fabrication process optimizations and subsequent experimental demonstrations leading towards cost-effective, energy-efficient and high-speed silicon photonic circuits for various applications. As of now, various prototype and packaged devices like power splitters, channel interleavers, variable optical attenuators, p-i-n phase shifters/modulators, ring resonators, DBR (Distributed Bragg Reflector) and SWG (Sub-Wavelength Grating) filters etc., have been demonstrated by utilizing the resources at our centre of excellence CPPICS and nanofabrication facilities at IIT Madras.

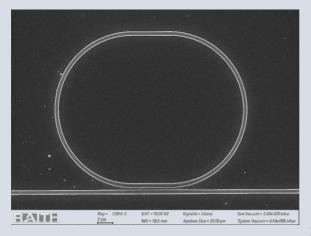

SEM top view of a Micro Ring Resonator on SOI

SEM top view of SWG Taper on SOI

SEM top view of grating coupler on SOI

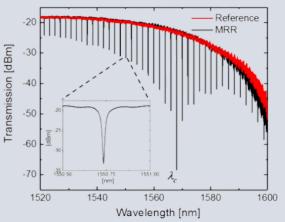

Measured transmission characteristics of a Micro Ring Resonator along with a reference waveguide

SEM top view of SWG waveguide on SOI

SEM top view of 2-D grating on SOI

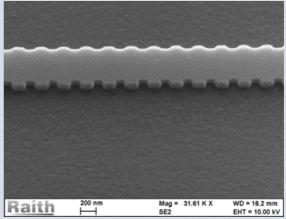

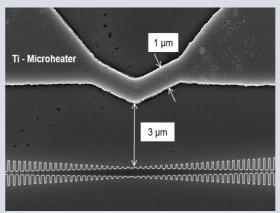

To address the fabrication imperfections and to operate these devices at specific working points or to switch between different states, active control is essential. One way is to use thermo-optic modulation by placing micro-heaters either at the side or on top of the waveguides and using heating to change the refractive index. Fabrication of these heaters starts once the passive devices are patterned. Since positioning of the heaters demand high precision, we use E-beam lithography. Aluminium (Al) is used for contact padS and Titanium (Ti) for metal heater fabrication. Below we have shown a MicroRing Resonator (MRR) of  $50\mu m$  ring radius with side Titanium (Ti) side heater.

SEM angled view of DBR on SOI

SEM zoomed-in view of MRR with side heater

SEM top view of MRR with side heater

SEM zoomed view of DBR cavity with side heater

# SiN Waveguide Technology

Associated Research Scholars: Riddhi Goswami, Pranita Ku. Swain, Anushka Tiwari, Sarad S. Bhakat

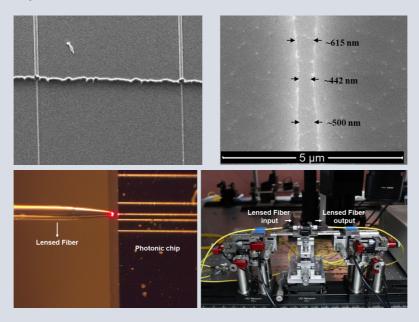

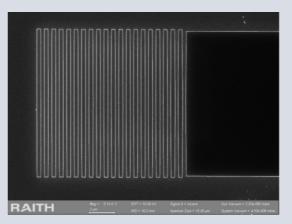

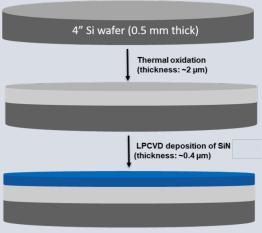

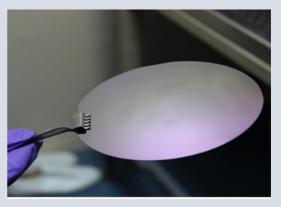

In addition to Si core, SiN (Silicon Nitride) is gaining major attention due to its relatively lower waveguide losses, wider transparency and less sensitivity to temperature fluctuations and fabrication variations. The growth of an optical grade oxide layer (for bottom cladding) and subsequent deposition of SiN device layer are the most important aspects for the realization of large-scale photonic integrated circuits with acceptable waveguide losses and fabrication yields. Our group has been working towards fulfilling that goal and has made conceivable achievements so far. We are able to grow good quality thermal oxide wafers( $\approx$  $2\mu m$ ) and stoichiometric, crack-free SiN wafers( $\approx$  $0.4\mu m$ ) with excellent wafer scale variations.

SiN Deposition Process Flow

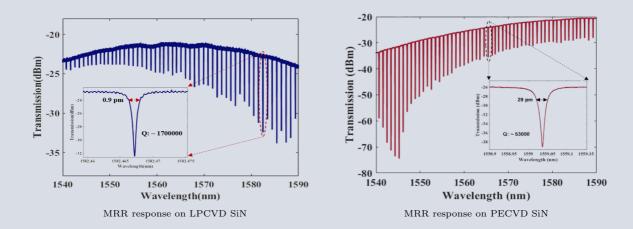

We have also been able to demonstrate losses below 1 dB/cm and 3 dB/cm in LPCVD (Low Pressure Chemical Vapour Deposition) and PECVD (Plasma Enhanced Chemical Vapour Deposition) SiN platforms (both on  $2\mu m$  thermal oxide) respectively using traditional waveguide technology like the SOI process which involves patterning on device layer. Both the platforms were developed completely indigenously here at IITM starting with 4 inch bare Si wafer.

Loading of thermal oxide wafers in SiN furnace

In-house fabricated SiN wafer

Although LPCVD SiN provides low-loss waveguides, the thickness is limited to 400 nm due to tensile stress within the film. However in order to harness the nonlinear properties of SiN, we need relatively thicker films for demonstrating applications such as frequency comb generation. We have

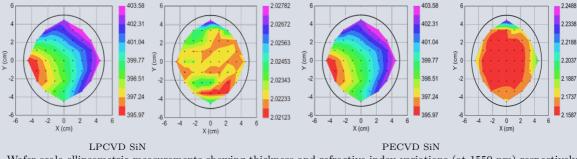

Wafer scale ellipsometric measurements showing thickness and refractive index variations (at 1550 nm) respectively

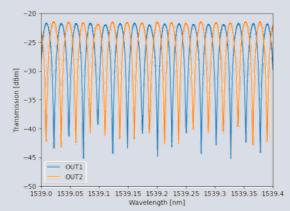

also, already established a process flow for Damascene which can provide efficient stress control and prevent cracks in the film (for higher thickness of SiN, >400 nm). The process is based on first etching trenches into buried oxide (BOX) layer and then filling the trenches with SiN for waveguide core and finally planarizing the surface with Chemical Mechanical Polishing (CMP). A top oxide layer may be deposited later depending on requirements. Damascene is expected to give lesser waveguide losses since we are not directly etching the SiN device layer leading to improved side-wall roughness. Low loss, planar optical waveguides have the potential to be a key enabling technology for a wide range of applications, such as delay lines, ultra narrow linewidth lasers, nonlinear photonic devices such as soliton Kerr frequency combs or quantum photonic circuits. Below attached are the MRR (Micro Ring Resonator) responses on the two different SiN platforms (fabricated with standard waveguide technology that involves etching of device layer).

# Si/SiN Hybrid Waveguide Technology: In-House Process Development

Associated Research Scholars: Sarad S. Bhakat, Riddhi Goswami, Anushka Tiwari, Pranita Ku. Swain.

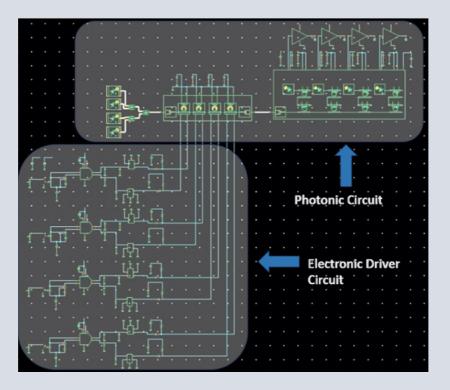

The rapid development of fabrication techniques has boosted the resurgence of silicon-based Photonic Integrated Circuits (PICs). The silicon-on-insulator (SOI) and Silicon Nitride (SiN) platforms have been extremely successful in PIC development due to their CMOS compatibility. The devices are usually fabricated on a wafer following a planar process, where only one core material with a defined thickness is included. This traditional single-material platform cannot provide all the functionalities required for fully integrated PICs. By embedding thin-film SiN onto the SOI platform, Si/SiN hybrid photonic devices can be integrated on the same chip, simultaneously leveraging the advantages of both material platforms.

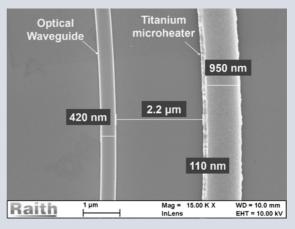

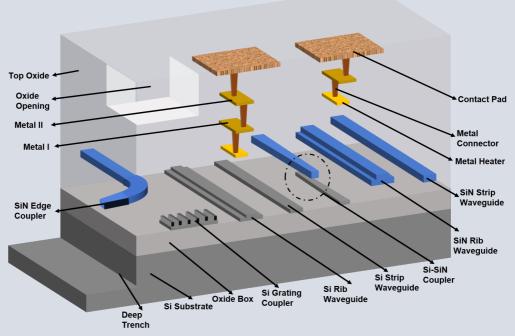

3D schematic representation of a hybrid Si/SiN photonic integrated circuit (PIC) Platform

Currently in PIC material technologies, no waveguide material can address the needs of all the potential applications of PICs. Therefore advanced PICs may require the best possible performance of a large number of different photonic elements in PICs to achieve the desired functionalities, which may not be possible with single waveguide material technology. The above figure showcases a 3D schematic of a hybrid Si/SiN photonic integrated circuit (PIC) designed for advanced optical and photonic applications. Key components include SiN strip and rib waveguides, Si strip and rib waveguides, and Si-SiN couplers that enable efficient light transmission and coupling between waveguide layers. The deep trench enhances isolation, while grating couplers and edge couplers facilitate light input/output. The metal heater assembly, with connectors and contact pads, ensures precise thermal control critical for tuning optical properties. Oxide layers provide electrical insulation and mechanical stability. This hybrid design combines silicon's compactness with silicon nitride's low-loss characteristics, making it ideal for high-performance photonic systems.

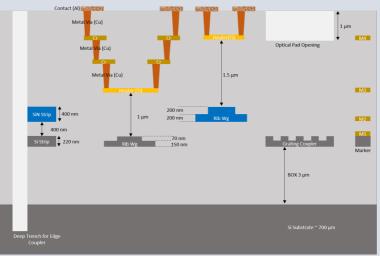

Cross-sectional view of a hybrid Si/SiN photonic integrated circuit (PIC)

This cross-sectional schematic highlights the intricate structure of a hybrid silicon-nitride photonic integrated circuit (PIC), emphasizing its multi-material integration. The diagram showcases SiN strip waveguides designed for low-loss optical routing, Si rib and strip waveguides for compact light confinement, and grating couplers for seamless light coupling. A deep trench ensures effective edge coupling, while the titanium metal heater, supported by chromium and copper vias, enables precise thermal tuning. The buried oxide (BOX) layer and silicon substrate provide the foundation for thermal insulation, mechanical support, and optical stability, enabling the hybrid PIC's high performance. distinct advantages over single-platform devices in two key applications. First, high-speed modulators and photodetector arrays can be fabricated on the well-established Silicon-on-Insulator (SOI) platform, widely recognized for its efficiency in active modulation. Second, for passive components like routing waveguides and delay lines, the lowloss characteristics of SiN material significantly enhance performance. These hybrid devices combine the strengths of both materials, minimizing optical losses, reducing power consumption, and enabling advanced high-density integration for PICs.

Hybrid Si/SiN integrated photonic devices offer

| Wavelength range                       | 0.3 µm – 3 µm | 1.1 μm – 4.5 μm |

|----------------------------------------|---------------|-----------------|

| asers, Amplifiers                      | NA            | NA              |

| Photodetectors                         | NA            | ++              |

| Modulators                             | NA            | +               |

| Thermo-optic phase shifter             | ++            | +++             |

| ow-loss passive devices                | +++           | ++              |

| Fiber to chip coupling                 | +++           | ++              |

| Packaging                              | +++           | +++             |

| Electronic-Photonic Co-<br>integration | +++           | +++             |

+++ : excellent, ++ : very good, + : good

# **Photonic Circuits and Processors**

Photonic circuits have diverse applications, spanning from Programmable Photonics, featuring versatile photonic processors, to Microwave Photonics, incorporating RF filters and optoelectronic oscillators. They also find applications in Quantum Integrated processors, which utilize photon sources, Quantum random number generators, Quantum key distribution, and Quantum processors.

# Active devices: Modulators and Photodetectors

# Associated Research Scholars: Suvarna Parvathy, Pawan Kumar

Modulators and photodetectors are major components in any integrated photonic circuit, performing the electrical-optical and optical-electrical conversion of signals respectively. It is essential to have high efficiency and high bandwidth modulators and detectors for efficient and ultra-fast signal processing applications.

Modulation of light in silicon platform can be achieved by plasma or free carrier dispersion. The widely used modulation element is a waveguide with a p-n junction doped on it, which is operated under reverse bias. The application of voltage to the diode changes the free carrier concentration and thus the effective refractive index of the waveguide. This in turn results in a shift in the optical transmission characteristics of the device. The p-n doped waveguide or the p-n phase shifter can be integrated into various photonic devices like Mach-Zehnder Interferometer (MZI), Microring Resonator (MRR), Microdisc Resonator (MDR) to form respective modulators - MZM, MRM, MDM etc. Devices like distributed Bragg reflectors, photonic crystals have also been used for implementing modulator. Some of the important performance metrics of modulators are bandwidth, phase efficiency, extinction ratio, insertion loss, modulation amplitude, and footprint. As compared to interferometric modulators like MZM, resonant-based modulators like MRM, MDM have much lesser footprint and become a preferred choice for wavelength division multiplexing (WDM) applications.

Layout of microring, microdisc modulators fabricated from SilTerra

15 10

Microscopic image of all-pass ring modulator (10  $\mu m$  radius) fabricated from IMEC

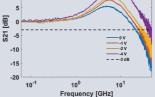

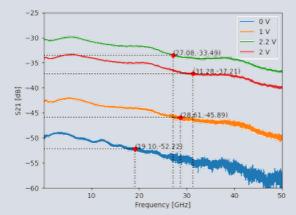

Electro-optic S21 response of MRM for different reverse bias voltages fabricated from SilTerra

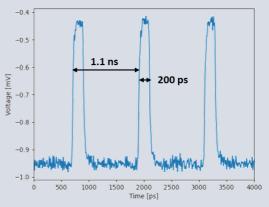

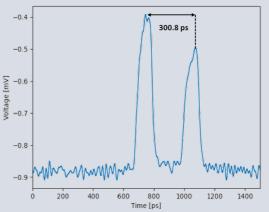

We have fabricated compact microring modulators of 5  $\mu m$  radius, and microdisc modulators of 10  $\mu m$  radius from IMEC, Belgium as well as SilTerra, Malaysia that can operate up to 50 GHz. The 3 dB cut-off frequency of a microring or microdisc modulator is largely decided by the quality factor of the device, and the RC time constant of the p-n junction. As the reverse bias on the p-n junction increases, the cut-off frequency of the modulator also increases, since the time constant decreases.

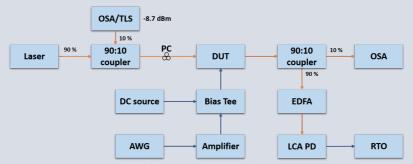

Experimental set-up for OOK modulation. OSA: Optical Spectrum Analyzer, TLS: Tunable Laser Source, DUT: Device Under Test, EDFA: Erbium Doped Fiber Amplifier, AWG: Arbitrary Waveform generator, LCA: Lightwave Component Analyzer, PD: Photodetector, RTO: Real Time Oscilloscope

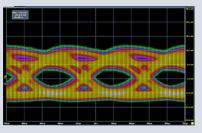

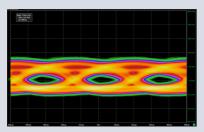

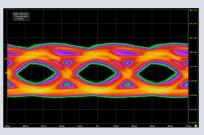

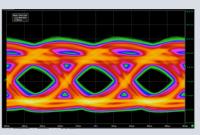

Digital on-off keying (OOK) modulation was studied at 10, 20, 25 Gbps speeds using a PRBS7 pseudo random sequence from an arbitrary waveform generator. It was observed that at higher input optical power, the modulation amplitude of the modulated eye diagram increases. The modulation amplitude degrades as speed of the signal increases as expected due to the low-pass frequency response of the modulator.

Eye diagram of microring modulator (IMEC) at 20 Gbps at low optical power (y-scale: 10 mV/div)

Eye diagram of microring modulator (IMEC) at 25 Gbps at low optical power (y-scale: 10 mV/div)

Eye diagram of microring modulator (IMEC) at 20 Gbps at high optical power (y-scale: 20 mV/div)  $\,$

Eye diagram of microring modulator (IMEC) at 25 Gbps at high optical power (y-scale:  $10~{\rm mV/div})$

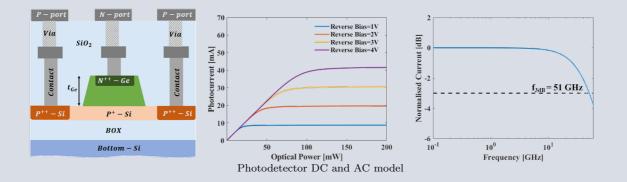

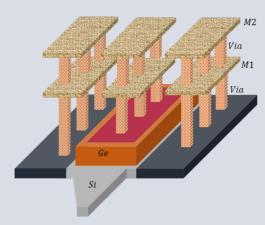

Silicon is transparent in telecommunication band (1310 - 1600 nm). Therefore, On chip detection in silicon photonics platform, we need another materials which can absorb light around above band and are compatible to CMOS fabrication process. Germanium is one, which is extensively used in silicon foundry for on chip detection. Recently, a variety of high-performance Ge photodetectors have been demonstrated on silicon photonic platforms by different research group using different silicon photonics foundries. Advancement of waveguide integrated germanium photodetectors (Ge PDs) holds crucial research significance for both academia and industry. The geometry and wavelength dependent characteristic of Ge photodetector has been comprehensively evaluated by our group in collaboration with Silterra, Malaysia. The measurement result show the low dark current, high responsivity, high bandwidth and high power saturation in single injection configuration. This study serves as a significant reference point to waveguide integrated photodetector in silicon photonics.

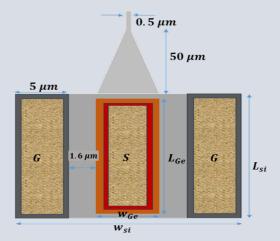

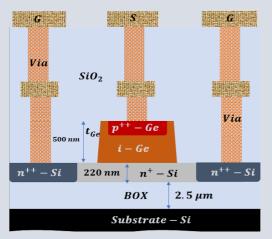

3D view of Ge on Silicon Photodetector

Top view of Ge on Silicon Photodetector

Cross-Section view of Ge on Silicon Photodetector

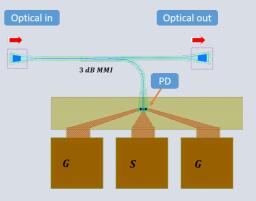

Complete Layout view of Ge on Silicon Photodetector with optical pad and MMI

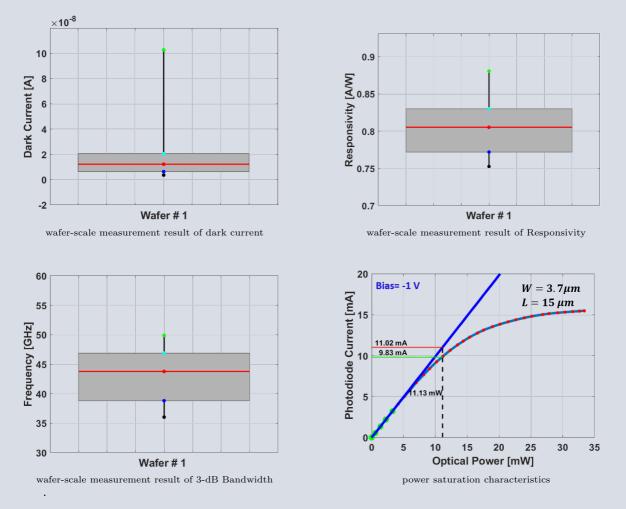

We have studied a vertical PIN Ge-photodetector of different length and width at full wafer level. All performance metrics has been evaluated. The main characteristic of the photodetector are Dark current, Responsivity, Bandwidth and current saturation. Dark current should be minimum as much as possible and Responsivity, Bandwidth and current saturation should be high as much as possible. But, there is always trade-off among these performance matrices. we can get higher Responsivity and current saturation by increasing device cross-section (upto some extend) but, as device cross-section increases, dark current increases and bandwidth decreases. We have analyzed the above performance matrices on 300 mm SOI wafer of device cross-section of 3.7  $\mu m \ge 15 \mu m$ . Most of devices shows low dark current of ~ 10nA and Responsivity of ~ 0.8A/W at reverse bias voltage of 1V. This depend on device geometry, operating wavelength and slightly on bias voltage. we also measured saturation characteristic of this device, which show maximum current of 16 mA and 1 dB compression of ~ 11mW optical power. Large bandwidth is required for high-speed data transmission. Our device shows 3 dB bandwidth of ~ 45GHz at a reverse bias voltage of 1V on full wafer scale.

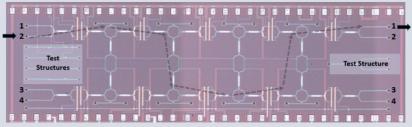

#### **Programmable Photonic Integrated Circuits**

#### Associated Research Scholars: Kumar Piyush, Yash Raj, Akash Shekhar, Ashitosh Velamuri, Pawan Kumar Pandit

Silicon photonics offers various methods to actively control or program the behavior of photonic devices through external stimuli such as electrical signals and local temperature changes. Leveraging these capabilities, Programmable Photonic Integrated Circuits (PPICs) provide a highly efficient platform for rapid prototyping, enabling multifunctional, upgradeable, and software-defined solutions. These features make PPICs instrumental in advancing diverse fields, including hardware accelerators, autonomous driving, neuromorphic computing, quantum technology, avionics, and next-generation communication systems such as 5G and beyond. In this context, we present our recent work on three key aspects of PPICs:

- 1. Study of NxN MZI meshes in feedforward configurations

- 2. Design and analysis of a 1x4 MZI with diode-integrated metal heaters

## 3. Exploration of recirculating mesh designs using square mesh architectures

#### Study of NxN MZI meshes in feedforward configurations

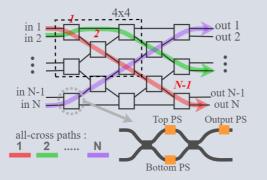

An  $N \times N$  MZI mesh consists of  $M \sim N^2$  phase-balanced MZIs, as shown in Fig. 1. Fabricationinduced waveguide variations introduce random phase errors in the MZIs. To counter these errors, correction is applied via the top or bottom phase shifter of each MZI. Efficient correction requires extracting the phase errors  $(\phi_1, \ldots, \phi_M)$  before programming the mesh to achieve the desired transmission and extinction at the output ports.

$N \times N$  MZI mesh highlighting all-cross paths, 4x4 MZI mesh (dotted), (inset) Tunable MZI structure for universal 2x2 unitary operation.

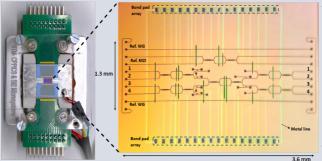

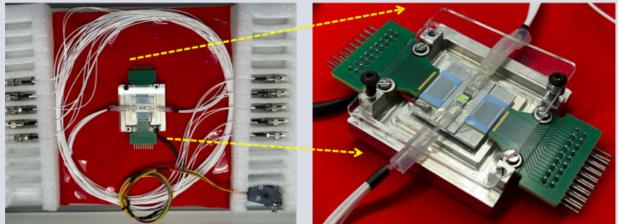

Electrically packaged 4x4 MZI mesh (consists of 5 MZIs), IMEC chip packaged at izmo Microsytems

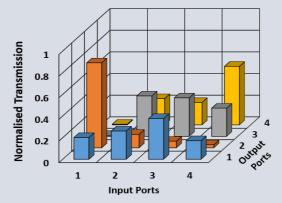

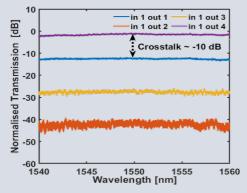

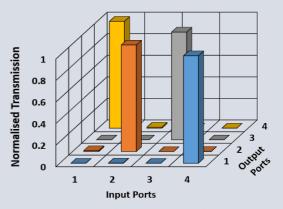

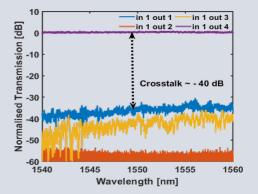

The phase errors  $(\phi_1, \ldots, \phi_M)$  are extracted from measured normalized passive optical transmissions using Particle Swarm Optimization (PSO). This is achieved by minimizing the estimation error between experimental measurements and corresponding theoretical values, summed over all inputoutput combinations. After correcting these phase errors by applying corresponding offset power, we observed a significant reduction in optical crosstalk to -40 dB. This reduction remained consistent across all input ports throughout the

Passive transmission of simulated mesh with introduced random phase errors of a  $4{\times}4$  MZI mesh

Normalized optical transmission output power of the packaged 4x4 MZI mesh upon characterization **be-fore** phase error correction

Passive transmission of simulated mesh after phase error correction using the algorithm.

Normalized optical transmission output power of the packaged 4x4 MZI mesh upon characterization **after** phase error correction

## Design and analysis of a 1x4 MZI with diode-integrated metal heaters

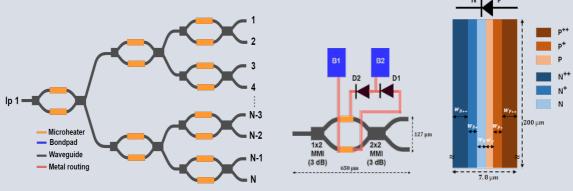

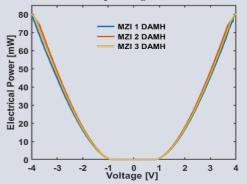

The  $1 \times N$  programmable power splitter uses a tunable  $1 \times 2$  MZI with Diode-Integrated Micro Heaters (DIMH) and two 3 dB splitters (IMEC PDK). A single bond pad enables bidirectional tuning by alternating the forward and reverse bias of the diodes.

$1{\times}\mathrm{N}$  power splitter design layout based on  $1{\times}2$  MZIs

$<sup>1{\</sup>times}2$  MZI scheme integrated with two diode-assisted microheaters and Diode design profile

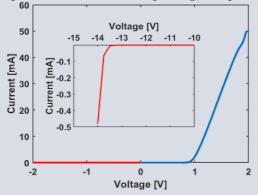

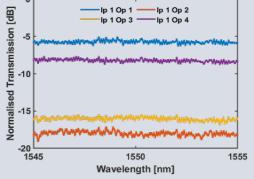

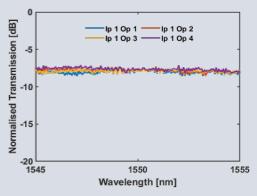

Bipolar driving for the DIMH, applying  $\pm 4V$  across three MZI-DIMH configurations, delivers 80 mW and reduces bond pad requirements by 50%. The normalized passive transmission for the 1×4 splitter shows non-ideal splitting, but phase correction achieves uniform splitting within  $\pm 0.25$  dB.

Experimental diode I-V characteristics (inset showing reverse breakdown voltage)

Non-uniform power splitting before phase error corrections

Electrical power delivered by Diode Assisted Metal Heater as a function of bias voltage: negative (positive) voltage for bottom (top) arm of MZIs

uniform power splitting characteristics after correcting phase errors

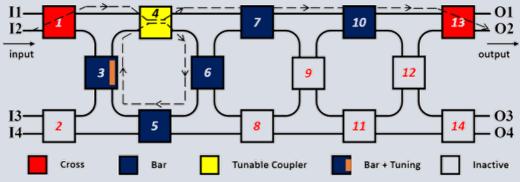

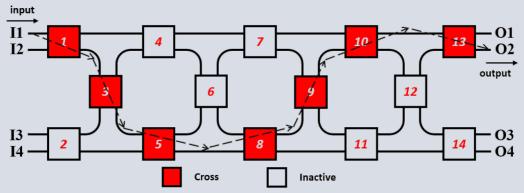

## Exploration of recirculating mesh designs using square mesh architectures

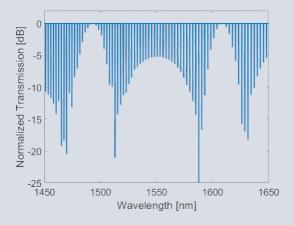

MZI-based feedforward designs are widely used for lattice filters and various photonic applications. However, realizing devices like microring resonators necessitates backward propagation, which can be achieved through a recirculating mesh architecture. To investigate this further, we fabricated a  $4 \times 4$ MZI-based recirculating mesh design with tunable MZIs, enabling multiple ring configurations, one of which is depicted below. By tuning the free spectral range of the ring formed within this square mesh, we successfully demonstrated the functionality of a multiband RF filter.

4x4 square mesh, fabricated at IMEC. Arrow showing the path followed by light input at port 2 to output at port 1

Schematic representation of the proposed PPIC to operate in a Microring Resonator configuration

Schematic representation of the programmable square mesh indicating an all-cross path from input I1 to output O2 (I1 $\rightarrow$ O2)

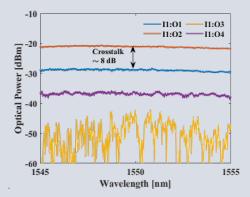

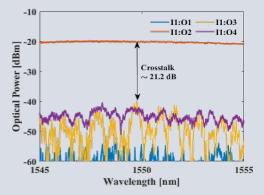

Fabrication-induced phase variations are unavoidable and can cause undesired crosstalk at the output ports. In one instance within the square mesh, with input at port 1, the initially measured crosstalk was -8 dB. After phase error correction, the crosstalk was significantly reduced to -21 dB, greatly improving the system's performance and signal quality. Following this correction, we successfully realized the ring resonator, enabling tuning of its coupling coefficient and resonance wavelength.

Measured optical power spectrum transmitted at the output ports before phase error corrections

Measured optical power spectrum for the selected path at all the output ports after phase error corrections

Thermo-optic tuning of MRR coupling coefficient in configuration-1  $\,$

Thermo-optic resonance tuning of MRR in configuration-1 for a given coupling condition

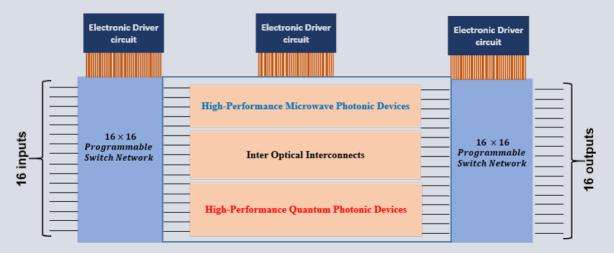

The future of programmable photonics shows great promise, particularly in emerging fields like neuromorphic computing and computing accelerators. Neuromorphic computing seeks efficient hardware and algorithms for tasks like pattern recognition and decision-making. Programmable photonics also offers substantial potential in high-performance computing and specialized computing accelerators designed to boost specific computational tasks. Integrating specialized high-performance photonic blocks within a central hub streamlines the incorporation of one or multiple modules. This central hub, featuring an NxN input and output switch, directed by external electronic drivers, transforms into a dynamic and versatile Multipurpose Programmable Photonic Processor, catering to a wide array of functions and applications.

Multipurpose Programmable Photonic Processor

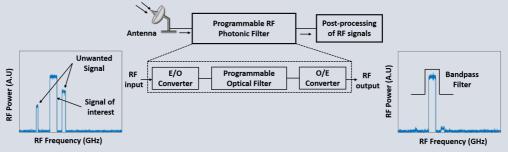

#### **Programmable RF Photonic Filters**

#### Associated Research Scholars: Ashitosh Velamuri, Kumar Piyush and Yash Raj

An RF filter is the basic component of any RF receiver architecture to separate the unwanted signal from the signal of interest. For this purpose, passive electrical filters are most commonly used because of their robustness and cost-effectiveness. However, these filters are designed to operate at a single frequency band with little to no scope for tuning and usually are power hungry especially at mmWave frequencies. The programmable RF photonic filters shows promise in terms of size, weight and power (SWaP), wide-band tunability and scalability, which are very crucial in 5G/6G and satellite communications and avionic applications.

General scheme of RF receiver, emphasizing the RF filter functionality.

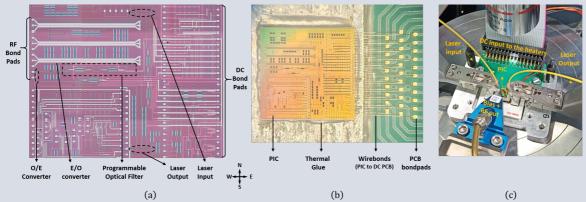

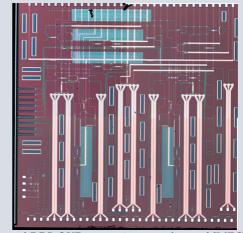

At CoE-CPPICS, we are working towards the development of a working prototype of a widely tunable (upto 40 GHz) RF photonic filter. We have proposed a novel operational scheme of the programmable optical filter to realize a tunable RF photonic filter with improved shape factor and a scope to realize multiple passband response. The photonics integrated circuit (PIC) with on-chip modulator, optical signal process and photodetector was designed at CoE-CPPICS, IIT Madras, fabricated at IMEC Belgium and electrically packaged at izmo Microsystems, Bengaluru (industry partner).

(a) Microscope image of the photonic integrated circuit (PIC) indicating the critical functional blocks, (b) microscope image of the PIC wirebonded to the DC PCB for multi-heater control, and (c) electrically packaged PIC probed with necessary optical, DC and RF connections during the experiment.

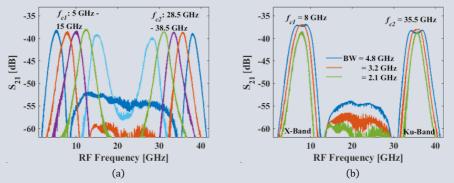

With the packaged PIC, a lab-level demonstration of the microwave photonic filter with two tunable passbands (5 GHz to 15 GHz and 28.5 GHz to 38.5 GHz) and a tunable bandwidth (2.1 GHz to 4.8 GHz) was done. For the full demonstration of the programmable microwave photonic filter, an RF interfacing printed circuit board (PCB) is critical block to feed-in and feed-out the signal from the filter module, which is currently a work in progress at CoE-CPPICS.

(a) Tunable two-band RF filter over 5 GHz - 15 GHz and 28.5 GHz - 38.5 GHz. Bandwidth = 2 GHz, (b) RF filter with tunable bandwidth (2.1 GHz - 4.8 GHz) at 8 GHz (X-band) and 35.5 GHz (Ku-band).

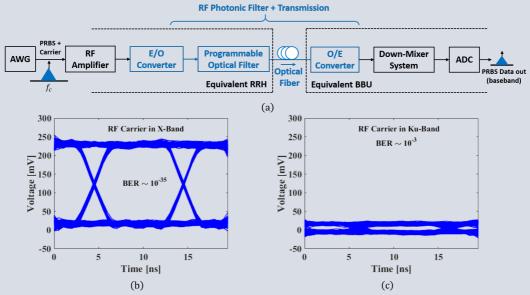

Recently, we have successfully performed a proof-of-concept evaluation of the feasibility of the integration of the microwave photonic filter in the wireless communication networks. For this purpose, an X-band radio-over-fiber receiver link of a wireless communication network was set up at CoE-CPPICS and an efficient simultaneous data transmission and filtering operation was realized with an excellent bit-error-rates of  $10^{-35}$  for the RF carrier aligned with the central frequency of the microwave photonic filter.

(a) Schematic representation of the programmable photonics integrated circuit (PPIC) based equivalent X-Band Radio over Fiber receiver link realized at CoE-CPPICS. AWG: arbitrary waveform generator, ADC: analog to digital converter, RRH: remote radio head and BBU: baseband unit, (b) eye diagram of transmitted data at the equivalent BBU with X-band RF carrier indicating an excellent BER of  $10^{-35}$ , (c) (b) eye diagram of transmitted data at the equivalent BBU with Ku-band RF carrier indicating a very poor BER of  $10^{-3}$ .

## Photonic Chip based Optoelectronic Oscillator

Associated Research Scholars: Anushka Tiwari, Ashitosh Velamuri

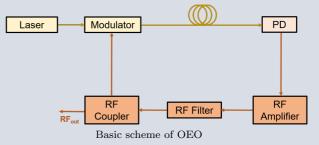

RF signal generation with low linewidth and phase noise is required in multiple applications such as radar systems, satellite communication and RF signal processing. This is mostly accomplished in bulk optics by frequency multiplication or longer low-loss delay line lengths. The optical modulated signal pass through a low loss fiber and detected in PD. Then the recovered modulated signal from the PD is amplified and pass through a bandpass filter to select frequency of operation by suppressing other cavity modes. Selected frequency of operation from RF filter is fed back to the modulator and forms an opto-electronic cavity leading to self-sustained oscillations once the loop gain exceeds the total loss of the loop. Nevertheless, optoelectronic oscillator (OEO) systems using the traditional method are large and susceptible to outside disturbances; also, a longer fiber delay line length produces a large number of closely spaced eigenmodes. It is challenging to find an electrical filter with these crucial narrowband and tunability requirements since a narrow bandpass filter is needed to choose a single oscillator mode in order to produce a spectrally pure RF signal.

The on-chip MRR using low loss waveguides offers high Q-value resonances and can be a promising alternative to realize narrowband microwave photonic filters and oscillators.

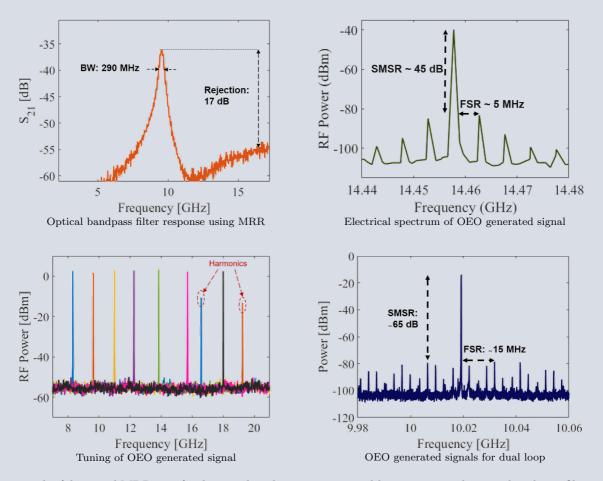

In CoE-CPPICS, we have demonstrated the narrowband RF photonic filter using high-Q MRR and the RF signal generation leveraging the same optical filter on silicon nitride platform. The SMSR of the signal generated is dependent on the filter bandwidth or FSR of the generated cavity modes. Hence, to achieve high SMSR ultra narrow band filter is needed or wider FSR of the cavity modes which depends on loop length with major contribution from fiber length used in loop.

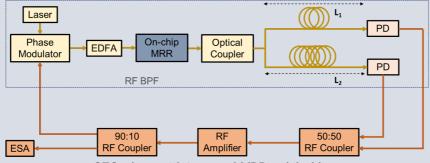

Therefore, to further enhance the SMSR and to enable single-mode selection, signal generation using a dual loop cavity has been demonstrated recently.

OEO scheme with integrated MRR and dual loop

In this scheme, RF signal is generated and filtered in the optical domain from the transient RF noise and looped back in electrical domain to the modulator. The central frequency of optical filter is decided from the difference between the laser wavelength (positioned near one of the resonances) and corresponding MRR resonance which would be phase matched peak frequency of oscillation for individual loops. We have designed and demonstrated low loss waveguides based high-Q ( $\simeq 1.7$  million) MRR on SiN platform using the in-house fabrication facilities of Centre for NEMS and Nanophotonics (CNNP), IIT Madras.

The fabricated MRR was further used to demonstrate tunable microwave photonic bandpass filters and oscillators. The observed filter response exhibits a minimum 3-dB pass bandwidth of  $\sim 290$  MHz with link gain of -35 dB. Using the narrow bandpass filter we have demonstrated microwave photonic oscillator which could be tunable upto 60 GHz (limited by the bandwidth of RF amplifier i.e. 20 GHz used in the experimental setup). Longitudinal cavity modes of the OEO have been resolved to measure the side mode suppression ratio of 45 dB with FSR of the cavity is 5 MHz.

Experiment has been further extended to increase the SMSR and FSR of the cavity using dual loop OEO. Two different fiber length is used for vernier effect where the frequency of oscillation and its FSR is decided by phase matched cavity modes in two loops. SMSR and FSR of the demonstrated dual loop OEO cavity is  $\sim 65$  dB and  $\sim 15$  MHz, respectively.

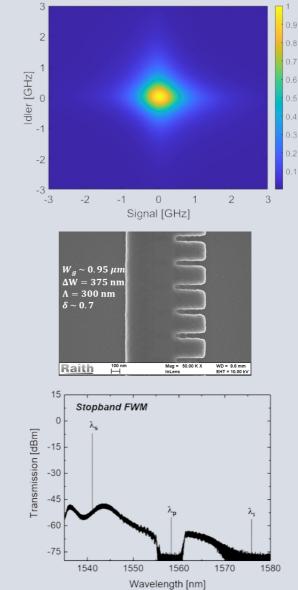

#### **Nonlinear Integrated Photonics**

# Associated Research Scholars: Arnab Goswami, Anushka Tiwari, Pranita Ku. Swain, Nagarajan Nallusamy

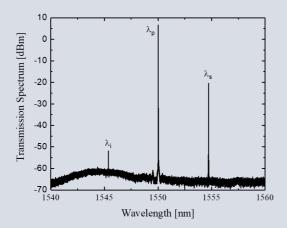

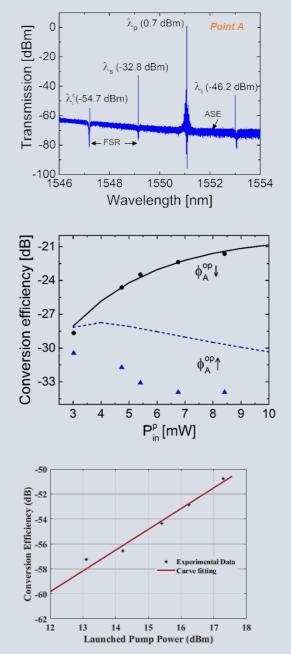

The distinctive attributes of nonlinear optical effects find practical utility within miniaturized photonic devices, enabling the manipulation of light in innovative and potent ways. CMOS-compatible integrated photonics holds significant promise across a spectrum of applications, including on-chip wave-length conversion, all-optical signal processing, parametric amplifiers, frequency combs, and photon pair generation. Our primary focus lies in utilizing four-wave mixing (FWM) for wavelength conversion in silicon and silicon nitride-based devices. Currently, we are actively engaged in research aimed at generating photon pairs and frequency combs within these integrated material platforms. The below figures illustrate the FWM spectrum and conversion efficiency in a 2 mm long silicon waveguide.

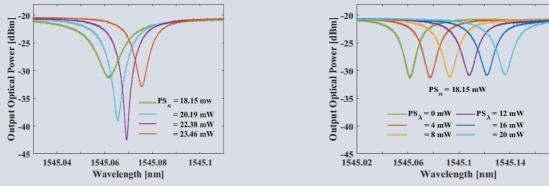

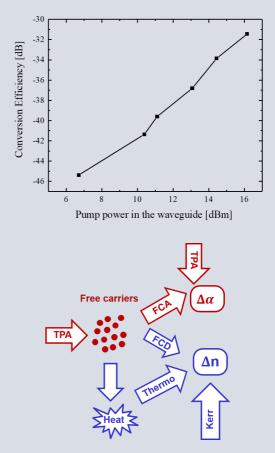

Compact microring resonator (MRR) with a suitably designed waveguide core in SOI substrate is an excellent device to enhance the field strength of a pump laser light for FWM based process. Nevertheless, optimizing silicon waveguides presents certain challenges, especially optical bistability due to self-phase modulation caused by the Kerr effect and mitigating the impact of two-photon absorption at communication wavelengths. This absorption subsequently leads to free carrier-induced plasma dispersion, making it crucial to address these issues to precisely control the strength of the pump field at resonance wavelengths with the phase shifter incorporated MRR.

Non-linear mechanisms at high power in silicon

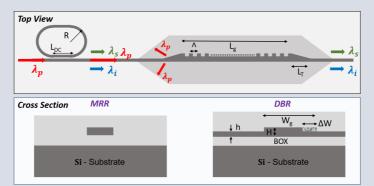

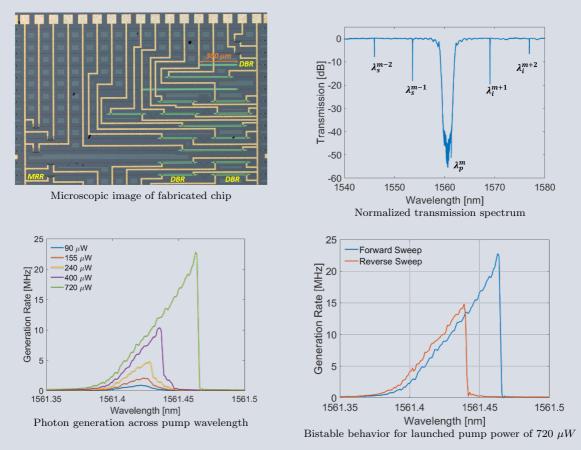

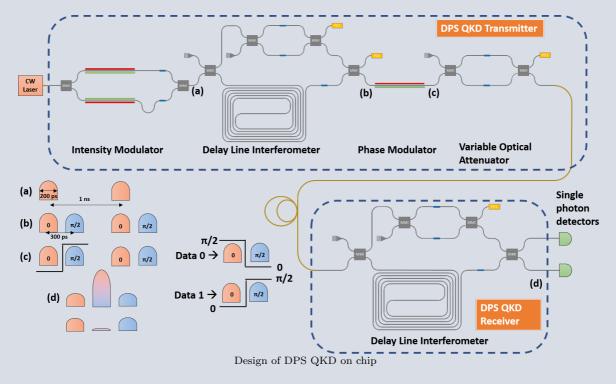

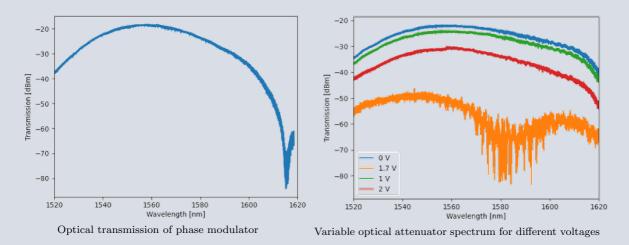

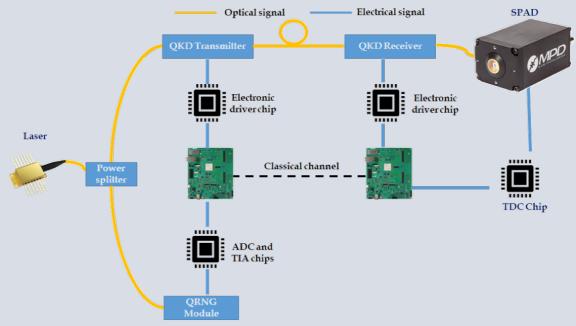

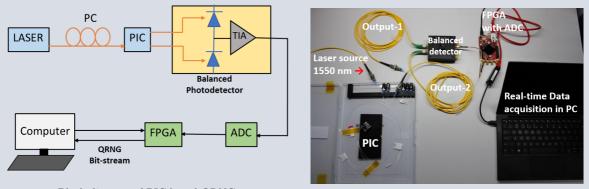

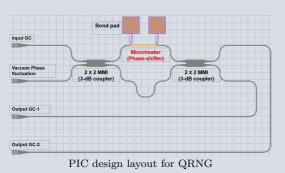

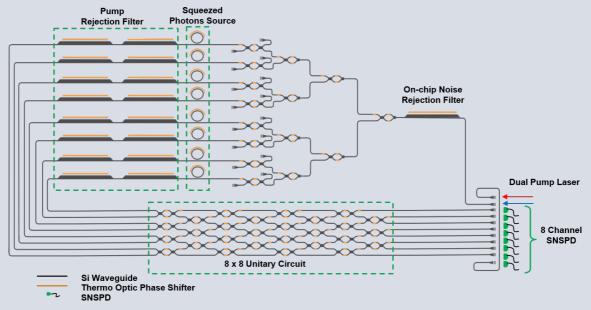

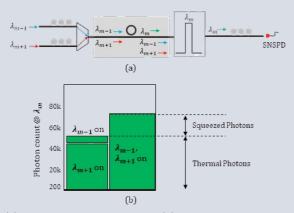

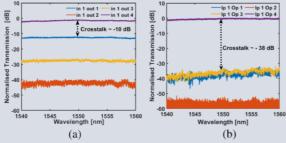

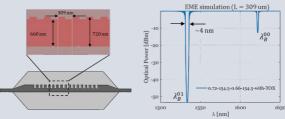

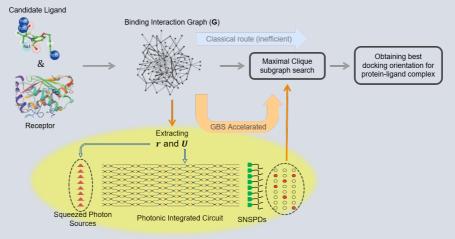

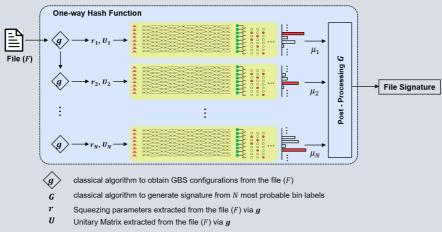

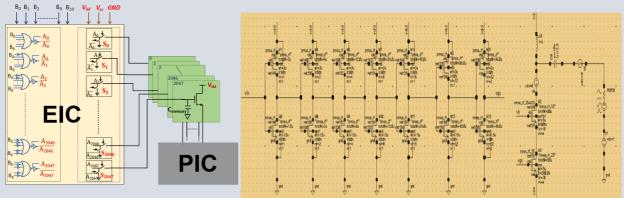

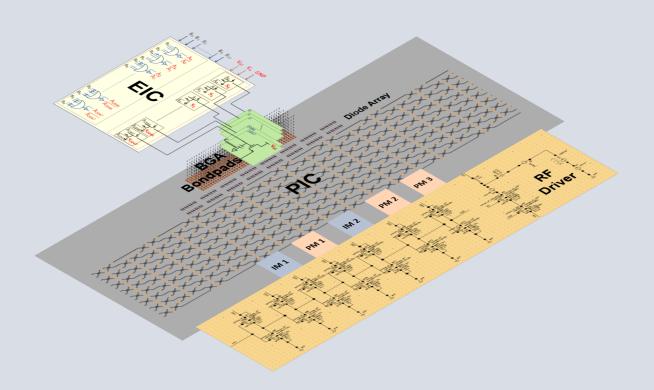

For a microring resonator of radius 50  $\mu m$ , an improved stimulated FWM gain of ~ 11.6 dB has been observed while thermo-optically blue-shifting resonances (point B) in comparison to that of